MicroZed Chronicles: SFP, SFP+ and QSFP

- Sep 24, 2025

- 4 min read

FPGAs are great, they allow us to process data at rates unachievable by any other means. However, this comes with a challenge: we need to be able to get data on and off the device to support that processing.

While the high-performance IO and XPIO of AMD devices are very capable of operating at high bandwidth, for some applications we need to operate much faster. This is where gigabit transceivers come into their own, allowing ultra-fast transmission and reception of data.

To get the best interfacing flexibility, these transceivers are often combined with interface modules that enable media-specific transceivers to be used.

What this means is that, depending on the application, we can use a specific interface module in our design. For example, if we are using 10G Ethernet, we can use a dedicated 10G interface module. The most popular of these interface module standards is the Small Form-Factor Pluggable (SFP), which you will find on both development and production boards.

If you are not familiar with it, an SFP module is a hot-pluggable interface module that allows us to connect gigabit transceivers with high-speed cables and fiber. The SFP standard used depends on the required data rate.

Before we look at the standards, let’s examine the signals provided on an SFP interface:

TX – Differential transmit data

RX – Differential receive data

I²C (SCL and SDA) – Serial interface providing information and configuration data on the SFP module

TX Disable – Driving this signal high disables the optical output

RX LOS – Indicates the receiver has lost lock

RS[0:1] – Optional rate select signals that enable a change of line rate

In the simplest FPGA implementation, we can easily connect to an SFP using a single transceiver and a couple of logic-level signals. The simplest design just needs TX Disable under control.

For SFP, each interface uses a single gigabit transceiver pair (TX and RX). In our solutions we are most likely to see either:

SFP+ – Supports line rates up to 10 Gbps

SFP28 – Supports line rates up to 28 Gbps

Standard SFP supports line rates of only 1 Gbps, so it is less common in high-speed FPGA applications. SFP28 is backward compatible with SFP+, but be careful with standard SFP modules, 1 Gbps is the minimum for SFP+ and SFP28.

Recently, we have been using SFP+ for several applications. We examined using SFP with the Exostiv probe, and we also looked at Aurora and Chip2Chip protocols.

One real-world application we developed recently uses Aurora to send XADC data as fast as possible from one device to another. The SFP provides the necessary electrical isolation by enabling transmission over fiber between Artix-7 FPGAs.

Of course, some solutions need line rates above 28 Gbps—for example, 100G Ethernet. In this instance, we can leverage multiple GT lanes and use a Quad Small Form-Factor Pluggable (QSFP) module.

In its base format, QSFP+ is designed to support four 10 Gbps lines, providing a 40 Gbps link. QSFP28 leverages four 28 Gbps lanes to implement 100 Gbps, ideal for 100G Ethernet. QSFP also offers line rates above 28 Gbps, supporting up to 400 Gbps using QSFP112, which leverages four 112 Gbps lanes as provided by Versal Premium GTM transceivers.

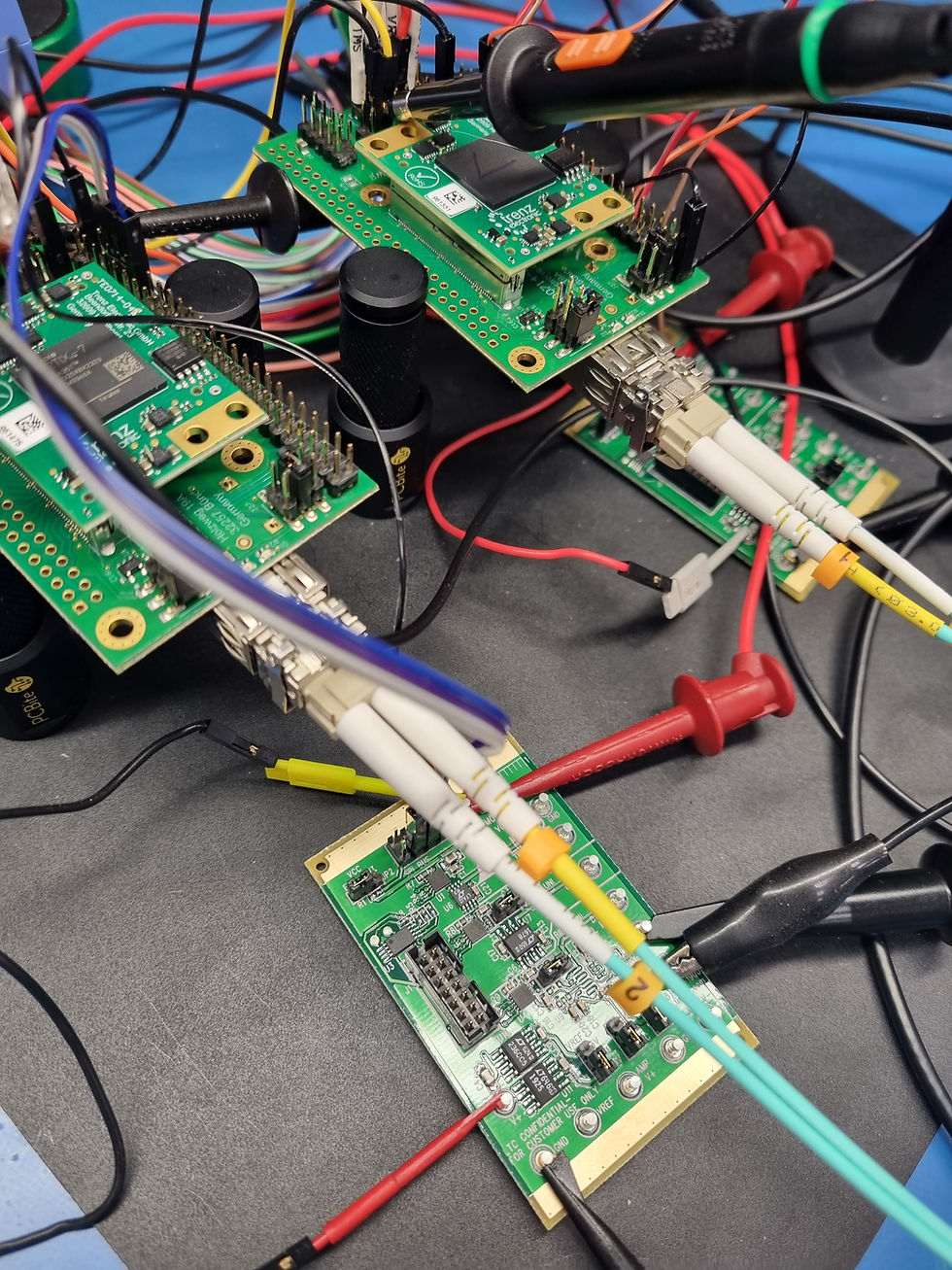

Looking across the development boards in the lab, several of them contain a wide variety of SFP and QSFP configurations.

As SFP+/SFP28 and QSFP are very common in the FPGA world, it is always a good idea to have some SFP/QSFP loopback modules available in the lab for testing. These enable us to clearly and easily see if links are established without the need for a second board. We can, of course, do internal loopback, but the board is only truly tested if we loop back at the connector.

UK FPGA Conference

FPGA Horizons - October 7th 2025 - THE FPGA Conference, find out more here.

Workshops and Webinars:

If you enjoyed the blog why not take a look at the free webinars, workshops and training courses we have created over the years. Highlights include:

Upcoming Webinars Timing, RTL Creation, FPGA Math and Mixed Signal

Professional PYNQ Learn how to use PYNQ in your developments

Introduction to Vivado learn how to use AMD Vivado

Ultra96, MiniZed & ZU1 three day course looking at HW, SW and PetaLinux

Arty Z7-20 Class looking at HW, SW and PetaLinux

Mastering MicroBlaze learn how to create MicroBlaze solutions

HLS Hero Workshop learn how to create High Level Synthesis based solutions

Perfecting Petalinux learn how to create and work with PetaLinux OS

Boards

Get an Adiuvo development board:

Adiuvo Embedded System Development board - Embedded System Development Board

Adiuvo Embedded System Tile - Low Risk way to add a FPGA to your design.

SpaceWire CODEC - SpaceWire CODEC, digital download, AXIS Interfaces

SpaceWire RMAP Initiator - SpaceWire RMAP Initiator, digital download, AXIS & AXI4 Interfaces

SpaceWire RMAP Target - SpaceWire Target, digital download, AXI4 and AXIS Interfaces

Embedded System Book

Do you want to know more about designing embedded systems from scratch? Check out our book on creating embedded systems. This book will walk you through all the stages of requirements, architecture, component selection, schematics, layout, and FPGA / software design. We designed and manufactured the board at the heart of the book! The schematics and layout are available in Altium here. Learn more about the board (see previous blogs on Bring up, DDR validation, USB, Sensors) and view the schematics here.

Sponsored by AMD