MicroZed Chronicles: Validating Your Custom Zynq Board Memory

- Mar 12, 2021

- 2 min read

Updated: Jun 27, 2025

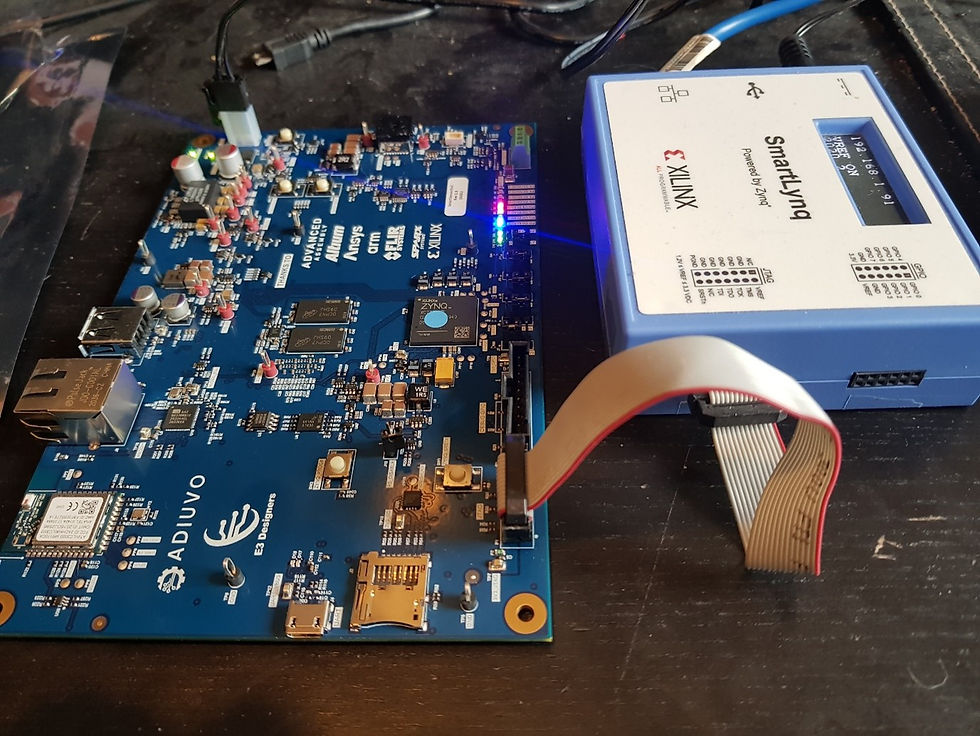

In the previous blog, we looked at how we could create a custom Vivado configuration for a Zynq PS on a custom designed board. The fun begins once we have created that configuration and built the BIT file because we need to ensure the configuration is correct and the software is executable on the processing system.

The approach we took here was simple. The first thing I wanted to do was to run a simple “Hello, World” application. At this point, we were still unsure the DDR was going to work because of either the Vivado PS DDR configuration or signal integrity and layout.

Of course, the former can be corrected but the latter is more of a fundamental issue. However, my co-author Dan Binnun spent considerable time on the analysis of the DDR during the design.

To get started testing the configuration of the custom Zynq board, I decided to run the project initially from the OCM. We can set up a simple “Hello, World” program to run from the OCM using the linker script.

Running this application successfully shows that we have at least some of the Zynq PS settings correctly. The next step, however, is to ensure the DDR is working correctly.

Thankfully, Vitis provides a DDR test program which also runs from the OCM and enables us to measure the eye diagram and the byte lane error rates on the DDR.

Creating the program is simple because it comes as one of the template applications in Vitis while using the embedded flow.

Once the project is compiled, we can run a debug session on our board to determine the DDR performance.

As the board has 1 GB of DDR memory, I ran the test on 1023 MB of the DDR memory. This would report any errors in each byte lane. The test does take a little time to complete because it is checking all 1 GB of the memory.

With the memory tested and no errors reported on any of the byte lanes, I wanted to check the eye diagram to see how open the eye is. An open eye will be critical to ensure the board is capable of functioning across all voltage, temperature, and operating conditions. If we have issues at room temperature while sitting on the bench, we will definitely have issues in the field.

The measurements show a 75% to 78% eye width, but how does this compare to other boards like the MicroZed and ZCU104, for example? To understand this, I generated projects for both the MicroZed and ZCU104 and ran the same DDR application on both boards.

Both boards showed eye widths between 69% and 78%, confirming that the 75% eye width of the custom defined board is well aligned with other similar designs.

Now that I know that the DDR works, I can start bringing up the board and testing it with more advanced interfaces because the necessary software can be executed from the DDR.

I will look at how we did this in a future blog in the coming weeks, it gets pretty exciting bringing up the petalinux OS and the remaining sensors.