top of page

All Posts

MicroZed Chronicles: Tria AUBoard 15P FPGA Development Kit

One of the great things about the FPGA world is the range of different development boards available to us. This diverse selection enables...

May 7, 20254 min read

MicroZed Chronicles: Lessons from bringing up Ethernet.

Over the past few weeks, I have been bringing up Ethernet on several different custom Kria systems. Each design utilized multiple GEMs...

Apr 30, 20254 min read

MicroZed Chronicles: Spartan 7 Tile and Simulink

We developed the Spartan 7 Embedded System tile as we thought it would be great for use in control plane applications. Of course the...

Apr 23, 20254 min read

MicroZed Chronicles: So what is Model based Engineering.

I have mentioned several times that I am a big fan of model based engineering especially for development of FPGA and embedded SoC....

Apr 16, 20255 min read

MicroZed Chronicles : Zephyr and MicroBlaze V

One of the most popular real time operating systems at the moment is Zephyr. Zephyr has a long history which stretches back to Virtuoso...

Apr 9, 20255 min read

Agilex™ 7 FPGAs and SoCs M-Series – DDR5

To support high-performance compute solutions, it is required not only to have high-performance logic but also the ability to interface...

Apr 7, 20253 min read

Agilex 7 FPGAs and SoCs M-Series – Examining the HBM2E Memory

Over the last few years, Altera has released several new FPGA devices. We have previously examined the Agilex™ 5 E-Series and the Agilex...

Apr 4, 20255 min read

MicroZed Chronicles: Vitis Heterogeneous System Design

One of the changes to tooling I have not written about to much is the Vitis Unifieds ability to create heterogeneous system designs, our...

Apr 2, 20255 min read

MicroZed Chronicles: Design Reuse

Recently, I was asked to present to a group of engineers about design reuse with respect to FPGA design. This is something which , as a...

Mar 26, 20255 min read

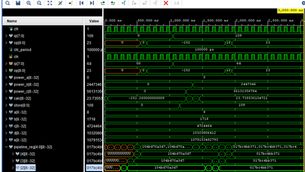

MicroZed Chronicles: Rounding

Programmable logic is great for implementing mathematical algorithms for a range of applications from filtering to machine learning....

Mar 19, 20254 min read

MicroZed Chronicles: GT Clocking architecture.

The ability to get data on and off chip, at high bandwidth is critical, we are fortunate that our FPGA provide a range of high...

Mar 12, 20254 min read

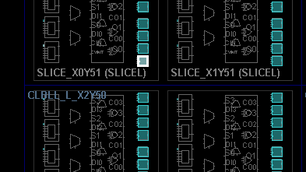

MicroZed Chronicles: Select IO Wizard and 7 series.

One of the great things about FPGAs is not only the configurable logic blocks, BRAMs, DSPs and a host of other useful peripherals but...

Mar 5, 20254 min read

MicroZed Chronicles: KR260 ROS and MicroRoS on MicroBlaze

A few weeks ago I was on a call with a one of the industrial architects at AMD Tomas Thoresen who mentioned he was working on a series of...

Feb 26, 20253 min read

MicroZed Chronicles: Shift Registers

Next to a simple register, a shift register is one of the simplest synchronous structures we may want to include within our FPGA designs....

Feb 19, 20254 min read

MicroZed Chronicles: Power Estimation vs Reality

Designers are well aware of the acronym SWaP-C, which relates to the Size, Weight, Power and Cost. FPGAs can be very useful in assisting...

Feb 12, 20254 min read

MicroZed Chronicles: Versal AI Edge, VESA LCD Display.

I have had the Alinx VD100 Versal Edge AI platform for a little while now. A few weeks ago, I set it up in my office so that I could...

Feb 5, 20255 min read

MicroZed Chronicles : Zynq, MicroBlaze, answering a question

One of the great things about writing this blog (there are many) is when people as real world questions as they need help. Last week,...

Jan 29, 20254 min read

MicroZed Chronicles: State Machines

I always remember when I was learning digital electronics at university, the lecturer John Rowe passing comment that a professional would...

Jan 22, 20255 min read

UK FPGA Conference

A few days ago, I posted on LinkedIn, X, and Reddit/fpga about the idea of hosting a UK FPGA conference later in the year. I believe...

Jan 18, 20253 min read

MicroZed Chronicles: Sliding Window Filter

One of the things I really enjoy is creating image processing solutions as you might notice from the projects I publish on Hackster. My...

Jan 15, 20255 min read

bottom of page