top of page

MicroZed Chronicles: Advanced SelectIO Logic Resources

Last week we looked at IDELAY2 and ODELAY2 in 7 series IO, the selectIO which is included in 7 Series, UltraScale and UltraScale+...

Feb 23, 20223 min read

MicroZed Chronicles: Scripting Vivado

Throughout the nine years I’ve been doing this blog, the majority, if not all, of the examples and Hackster projects have been...

Jan 26, 20223 min read

MicroZed Chronicles: Versal Part One

One of areas I started to explore last year, but never got chance to write more than a single blog on was Versal and the VMK180...

Jan 5, 20223 min read

MicroZed Chronicles: High-Level Synthesis Interfacing

High-Level Synthesis can provide us a significant advantage when we are working in the data plane (e.g., signal / image processing and...

Dec 15, 20213 min read

MicroZed Chronicles: Porting SpaceWire from Spartan-6 to Spartan-7

Space electronics is one of the main areas my consultancy is very active. SpaceWire is a differential high-speed communications protocol...

Dec 8, 20213 min read

MicroZed Chronicles: Bluespec RISC-V

There are several FPGA use cases where a softcore processor is beneficial to the overall solution. These can include anything from...

Sep 29, 20214 min read

MicroZed Chronicles: Working with the Kria SOM in Vivado

The Kria KV260 Vision AI Starter Kit is great for embedded vision applications and AI acceleration. Several of my clients, however, have...

Aug 25, 20214 min read

MicroZed Chronicles: Example Designs in Vivado and Vitis

Over the years, several blogs and projects have leveraged the Vivado and Vitis ability to generate example projects. One of the most...

Aug 4, 20212 min read

MicroZed Chronicles: A Blast from the Past!

Modern FPGA devices really spoil us. They include PLLs, DCM, DSP etc. and a range of interfaces that significantly ease our developments....

Jun 23, 20214 min read

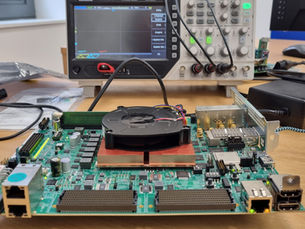

MicroZed Chronicles: Designing in DDR to your FPGA

Over the last two months, I have had several clients approach me for help regarding DDR3 / DDR3L interfaces that they have connected to...

Jun 16, 20213 min read

MicroZed Chronicles: Multi-Gigabit Transceivers

One aspect of FPGA design that we haven’t really examined is multi-gigabit transceivers (MGT). These transceivers are available in many...

Jun 2, 20215 min read

MicroZed Chronicles: Implementing Safe State Machines with Vivado

I thought I would examine how we can implement safe state machines when using Vivado 2020.2 and Xilinx synthesis

Dec 10, 20204 min read

MicroZed Chronicles: Using Analysis View in Vitis and Vivado

One of the most useful views available in both Vivado HLS and Vitis HLS is the analysis view.

Nov 18, 20203 min read

MicroZed Chronicles: Free Virtual Workshops On-Demand

This past summer, I was lucky to present several detailed virtual workshops on Vivado, PYNQ, Vitis, and more. They are available on-demand.

Nov 12, 20203 min read

MicroZed Chronicles: AXI Stream Verification IP

The AXI Stream VIP is extremely useful when we want to generate signal and image processing IP that use AXI Stream for interfacing.

Nov 5, 20203 min read

MicroZed Chronicles: Verifying AXI Peripherals

The designs we implement in Vivado often use AXI interfaces. These might be AXI Lite for configuration and control, AXI Memory Mapped

Oct 28, 20204 min read

Using SLX FPGA in Vitis bottom up flow

Last year, I examined SLX FPGA and used it to optimize IP Cores for implementation in Vivado looking at security and industrial algorithms.

Oct 19, 20204 min read

MicroZed Chronicles: Vivado Simulator Interface – Using C Test Benches on HDL

For complex algorithms, it is often a good idea to first create a model which defines the algorithm’s behavior.

Sep 30, 20204 min read

MicroZed Chronicles: Introduction to RTL Simulation and XSIM

No matter how captured (RTL, HLS, Model Driven), all programmable logic designs should start with agreed requirements that define the...

Sep 23, 20204 min read

MicroZed Chronicles: RTL Design Verification Techniques

So, before we look in more detail at Vivado XSIM, let’s first understand the entire verification landscape and what we are trying to achieve

Sep 17, 20203 min read

bottom of page