top of page

MicroZed Chronicles: 10 Years and 500 Posts

In September 2013, I was about to start a new role, as head of electronics at a space imaging developer when what should arrive in the...

Jun 21, 20235 min read

MicroZed Chronicles: A look at the DSP58

We looked at fixed point math a few weeks ago and we’ve also previously looked at how we can use DSP48 in both 7 series and UltraScale+...

Apr 19, 20233 min read

MicroZed Chronicles: Which Dev Board to Start With?

One of the questions I get asked a lot is which development board is the best for (beginner) FPGA and SOC development. Understandably,...

Mar 1, 20234 min read

MicroZed Chronicles: UltraScale+ IO, ODELAY3E and Cascading

We looked recently at the UltraScale+ IO resources which provide a range of capabilities that can be very effective in addressing both...

Dec 7, 20226 min read

MicroZed Chronicles: Free Webinars, Workshops, Tutorials and App Notes

One of my passions is sharing information about how we can develop better, more effective FPGA designs. This passion is the driving force...

Nov 23, 20223 min read

MicroZed Chronicles: Stream FIFO

A few months ago, we looked at the AXI Stream FIFO. The AXI Steaming FIFO allows developers to be able to access AXI Streams from AXI...

Nov 16, 20223 min read

MicroZed Chronicles: Video Frame Buffer Write

When I’ve previously created image processing blogs or applications, I have tended to use the Video Direct Memory Access (VDMA) module to...

Oct 19, 20223 min read

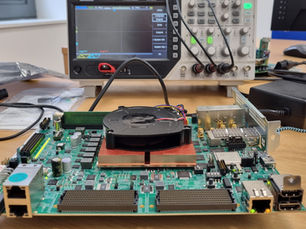

MicroZed Chronicles: MATLAB, Model Composer, and the Avnet ZUBoard

Over the last few weeks, I have been creating a course centered around the Avnet ZUBoard which will be like the MiniZed and Ultra96-V2...

Sep 28, 20222 min read

MicroZed Chronicles: Memory Scrubbing

One of the great things about the BRAM in Xilinx FPGAs is its ability to implement error correcting codes (ECC) on the data stored...

Aug 31, 20223 min read

MicroZed Chronicles: 10 Rules for HDL Development.

Writing good, portable, reusable HDL code, that enables the synthesized design to implement at the desired frequency can definitely be a...

Aug 23, 20224 min read

MicroZed Chronicles: Processor System to Programmable Logic Interrupts

One of the critical techniques in an embedded system that enables responsive software is using interrupts. In this series, we have used...

Jun 29, 20223 min read

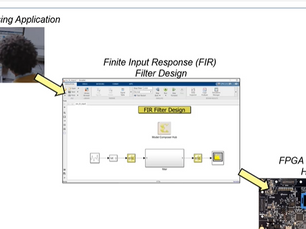

MicroZed Chronicles: Higher Levels of Abstraction

I am very interested in higher levels of abstraction for developing FPGAs and especially algorithms like image processing and control....

Jun 23, 20222 min read

MicroZed Chronicles: Synchronization & Metastability

Over the last week I noticed a few questions on r/FPGA and from a client on metastability and synchronizing signals coming into the...

Jun 8, 20223 min read

MicroZed Chronicles: Spartan-6 Migration Summary

Over the last few months, we have explored how to migrate from Spartan-6 FPGAs to 7 series and beyond in order to help developers with...

May 11, 20222 min read

MicroZed Chronicles: Using a DSP48E2 as a Multiplexer

I am a regular reader of many FPGA notice boards . A few days ago, I saw a question about how the DSP48E2 could be used as a...

May 4, 20226 min read

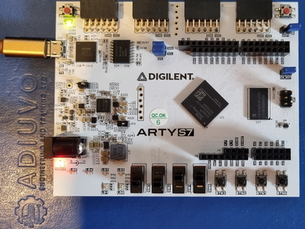

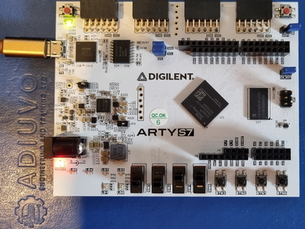

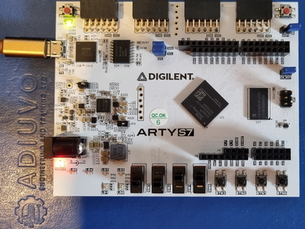

MicroZed Chronicles: AXI Stream FIFO IP Core

We looked at the AXI Virtual FIFO Controller in a blog a couple weeks ago and created an example design running on the Arty S7-50 while...

Apr 13, 20223 min read

MicroZed Chronicles: JTAG using a Raspberry Pi Pico

I’m a big fan of the Raspberry Pi Pico with the RP2040 microcontroller and have used it several times to emulate system interfaces on my...

Apr 6, 20223 min read

MicroZed Chronicles: AXI Virtual FIFO Controller

FIFOs are versatile tools to use within our designs because they enable us to buffer data when doing signal and image processing. We also...

Mar 30, 20223 min read

MicroZed Chronicles: Spartan 6 Q & A

A couple of week ago, I held several webinars on how to convert Spartan-6 designs into 7 series devices. There were several interesting...

Mar 9, 20222 min read

MicroZed Chronicles: Partial Configuration Introduction

Getting the most efficient utilization of our FPGA does not mean that we need to have the logic resources dedicated to all use cases. We...

Mar 2, 20223 min read

bottom of page