MicroZed Chronicles: How do you Architect Your Programmable Logic Designs?

- Aug 12, 2020

- 3 min read

Updated: Jun 27, 2025

In most of the blogs I write, I demonstrate or explain an FPGA or SoC design technique. This one, however, is going to be a little different because I am going to ask a question.

How do you architect your programmable logic designs?

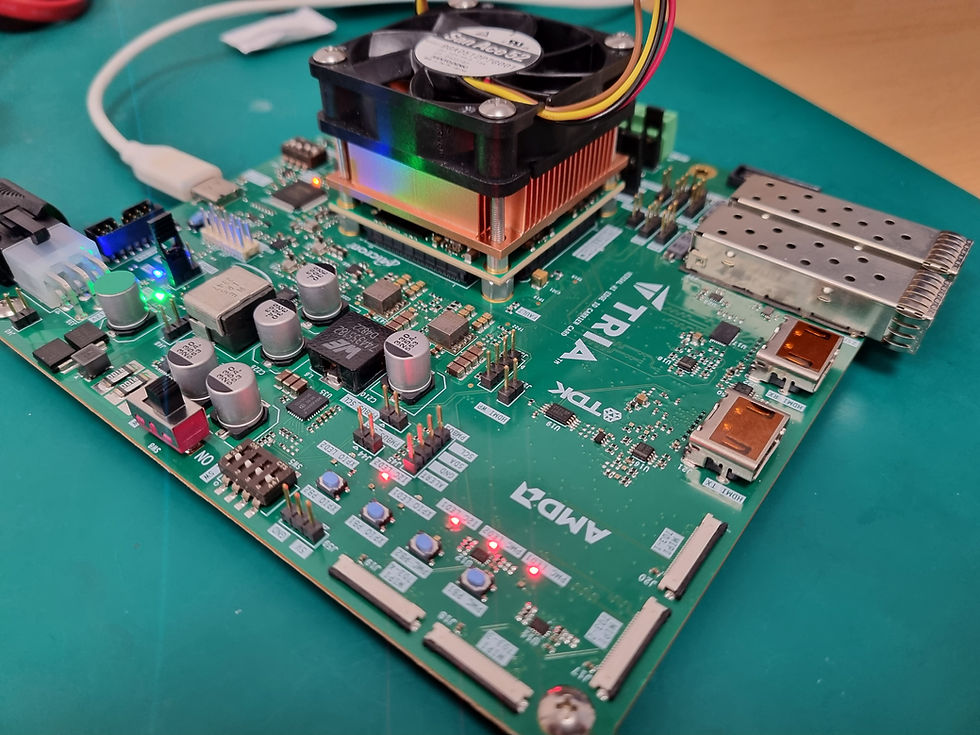

The question popped to mind as I was working on the architecture for three FPGAs as part of a satellite development. Of course, due to the end application, this architecture will be subjected to several reviews by both the prime contractor and appropriate space agency. Therefore, I want the architecture to show as much detail as possible without making the drawings difficult to maintain so that my design team can work from it with ease.

Architecting programmable logic designs can be complex so a good architecture will define several elements:

Modules required to implement the desired functionality. Of course, these modules may also contain hierarchy.

The clocks and clock enable each module receives. This begins to allow us to consider the clock domain crossing requirements if signals cross domains.

The reset each module receives. Like the clock, this allows us to consider the reset requirements for each module.

Interface signals interconnecting the modules in the architecture.

Efficient architectures and implementations leverage vendors’ existing IP cores wherever possible. It is also sensible to identify modules which can be reused across the architecture. A good example would be for a control algorithm or communications bus. I have three FPGAs to architect in the designs which prompted this question so identifying common modules will save a considerable amount of time in the development and verification process.

Interfaces are also another quick win as standardization enables the reuse of modules. Using standard interfaces such as AXI, AXI Stream, and APB for module interfaces also enables easy reuse of modules across several designs because the interfacing is not unique or made for a particular user. It may be that on this project, the IP core is not required to be reused but you may need the same function on a future development.

In my architecture diagrams for complex interfaces like ADC / DAC interfaces, AXI, or memory interface, I prefer to show an interface class type which wraps up and contains all the lower level signals. The interface classes and all signals can then be defined in the architecture document. This approach has several advantages. It keeps the architecture diagram simpler and enables modifications like signal addition or renaming to be performed only in one location.

When it comes to creating the architecture, my traditional approach is to start with a pen and paper and sketch out the main design blocks and key interfaces. Once that is completed, I capture the drawing using Visio to make it look more professional when included in the documentation.

Of course, this diagram needs to show all the signals and signal classes between the blocks. Ideally an engineer should be able to pick up the architecture and architecture document and start development or verification depending upon their role.

As I worked on my architectures, I was curious about how other engineers developed their programmable logic architectures so I asked the question across several FPGA discussion boards / forums.

The answers received where interesting indeed. Most of the respondents stated they used popular drawing packages including:

We can create nice architectural diagrams with all of these drawing packages. Interestingly, a couple people responded that they use Symbolator, which I was not familiar with.

Symbolator is a command line tool in Windows and Linux which will read VHDL and Verilog, component declarations, and generate a component diagram. This symbol can then be used in your preferred drawing package.

Installing Symbolator is straight forward. We can install it using pip and note that you may need to install some prerequisites including Pycairo, PyGObject and python-gi-cairo.

Once that is completed, you can create component symbols from component declarations in a range of different formats and presentation styles.

Since I was told about Symbolator, I decided that I would use it to capture the three architectures I was working on.

I really like how the blocks are created with clear definitions for the clock and data interface groups.

As it happens, I completed my architectures using Symbolator and Visio but I have a few ideas about how we might create a better architecture tool.

So, back to my initial question. How do you create your architectures?

See My FPGA / SoC Projects: Adam Taylor on Hackster.io

Get the Code: ATaylorCEngFIET (Adam Taylor)