top of page

MicroZed Chronicles: Cmod S7 & RTL Env Sensing

Sometimes I like to just sit and write RTL and try to create a simple project. Recently, I have been doing a lot of flying again. If you see me on a flight, you can be sure you are in for a turbulent experience, as it seems every flight I take is bumpy (sorry!). For a long while, I have been meaning to run a small experiment and create a compact, portable logging system which records acceleration, rotation, pressure, and temperature. I decided that I could do this using a sma

Feb 184 min read

MicroZed Chronicles: Accelerating FPGA Design Cycles with IP Cores and Open Libraries

The goal of professional FPGA development is to deliver projects on quality, on time, and within budget. Achieving this, however, can be...

Oct 16, 20243 min read

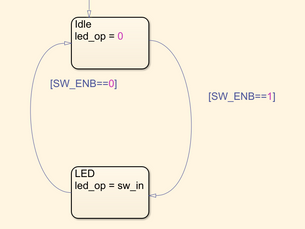

MicroZed Chronicles: Glitch Filtering

Our programmable logic designs are often deployed in applications which can be electrically noisy. This noise can affect the signals that...

Apr 5, 20234 min read

MicroZed Chronicles: Getting Started with Cocotb

Verification of both the modules and top-level testing is often more complex and time consuming than creating the HDL. Previously, we’ve...

Sep 7, 20225 min read

MicroZed Chronicles: 10 Rules for HDL Development.

Writing good, portable, reusable HDL code, that enables the synthesized design to implement at the desired frequency can definitely be a...

Aug 23, 20224 min read

MicroZed Chronicles: MATLAB / Simulink HDL Coder

A couple of weeks ago, I mentioned I had invested in MATLAB and HDL Coder to enable generation of RTL code directly from Simulink models....

Aug 10, 20224 min read

MicroZed Chronicles: Using a DSP48E2 as a Multiplexer

I am a regular reader of many FPGA notice boards . A few days ago, I saw a question about how the DSP48E2 could be used as a...

May 4, 20226 min read

MicroZed Chronicles: MicroBlaze in Spartan-6 (ISE/EDK) and 7 Series (Vivado)

Over the years, I have created MicroBlaze solutions for many Xilinx devices including Spartan-6, 7 series and up. Inserting a MicroBlaze...

Jan 12, 20223 min read

MicroZed Chronicles: GitHub Copilot

Programable logic is, of course, great for the implementation and acceleration of machine learning and artificial intelligence...

Nov 3, 20213 min read

MicroZed Chronicles: GHDL and UVVM Framework

In this post, we will expand the use of GHDL with an open-source verification framework for VHDL called UVVM.

Jan 14, 20213 min read

bottom of page