The Galaxia® development board provides users with a Certus™-NX LFD2NX-40 which is commercial equivalent of the Certus-NX-RT device offered by CAES.

This development board provides an excellent platform for the development of applications including

Deployment Cameras

Temperature Control Systems

Motor and Actuator Control

Telemetry and Telecommand processing

Health and Usage Monitoring

Radiation Beam Testing for design proving

Implementing Compression algorithms

Implementing Cryptographic security

The development board provides the user with the following Resources

Certus™-NX LFD2NX-40

80 IO accessible via PMOD

14 ADC Channels – Including ADC Reference

128 Mbit NOR flash for configuration

256 Kbit MRAM memory

100 MHz Oscillator

Lattice In-System Programmable Hardware Management Expander

RPi Pico

The Lattice Certus™-NX FPGA provides the user with 40K LUTs, 2.5 Mbit of BRAM, 56 DSP (18x18), 2 ADC and inbuilt 32KHz and 450 MHz Oscillators.

Board information such as Schematics, Assembly, STEP Files and supporting information can be found in the Bit Bucket Repository

It is also possible to deploy RISC-V processors on this development board, using the Lattice Propel tool. Examples of this can be examined in the tutorials below

Propel Builder Hardware Creation

Uniquely to this development board is the provision of the RPi Pico which provides the developer with a wide range of capabilities including.

Clock Generation – Generation of up to 65MHz reference clock using the PIO.

Communications emulation – Emulation of a differential backplane bus

Communications Monitoring – Monitoring and logging communications

Sensor emulation – Emulation of sensors across the system and implementation of failure modes

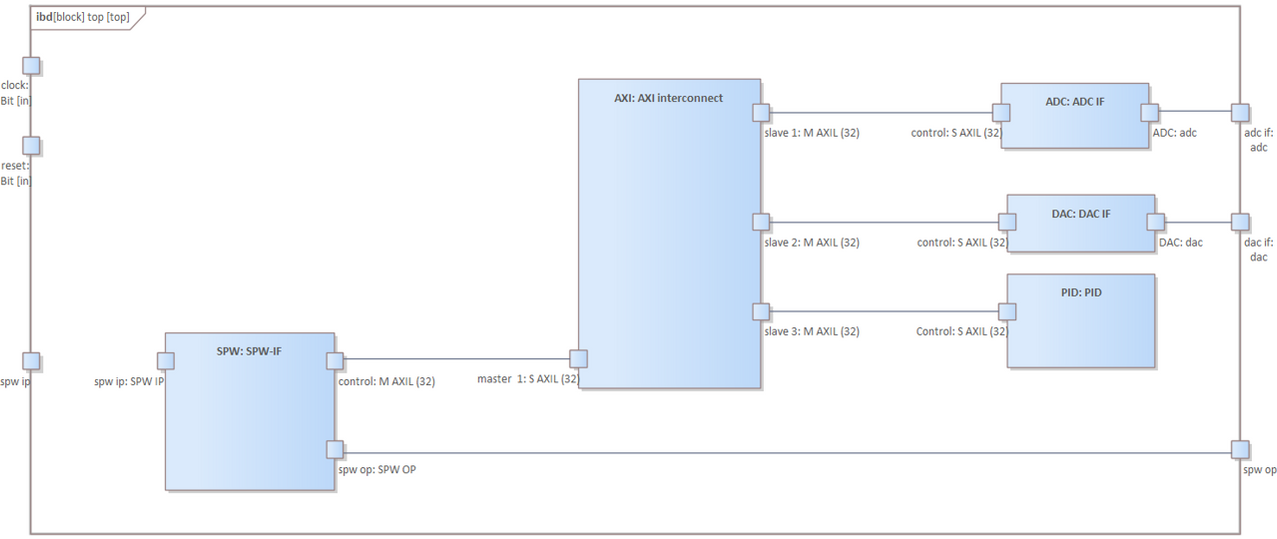

Complex communications creation – Implementation of a space wire communication protocol between the FPGA and the Pico. This provides a simple interface which can be controlled over the USB communication.

Power management and monitoring – Monitoring the power network, to control, monitor and observe the dissipated power as the FPGA design is used for anger or in under testing for example beam line.

These boards are available now! contact space@adiuvoengineering.com for more information on cost and lead times.